A New PCB Testing Technology

Nowadays, with the continuous emergence of products using LSI, it is more and more diffICult to install and test the corresponding PCB Although traditional online test technology is still used to test printed circuit boards, this method becomes more and more difficult due to the miniaturization and packaging of chips At present, a new test technology - boundary scan test technology has gradually developed. Most ASIC circuits and many medium-sized equipment have begun to use boundary scan test technology to design BST Technology complies with IEEE 1149.1 standard and provides a complete set of test solutions In practical testing, it does not need to resort to complex and expensive test equipment, and provides a test method independent of circuit board technology The advantage of using boundary scan test technology in integrated circuit design and Printed Circuit Board Design is that the test process is SIMple, which greatly shortens the test and diagnosis time, experiment, use and maintenance in the production process, thus greatly reducing the cost

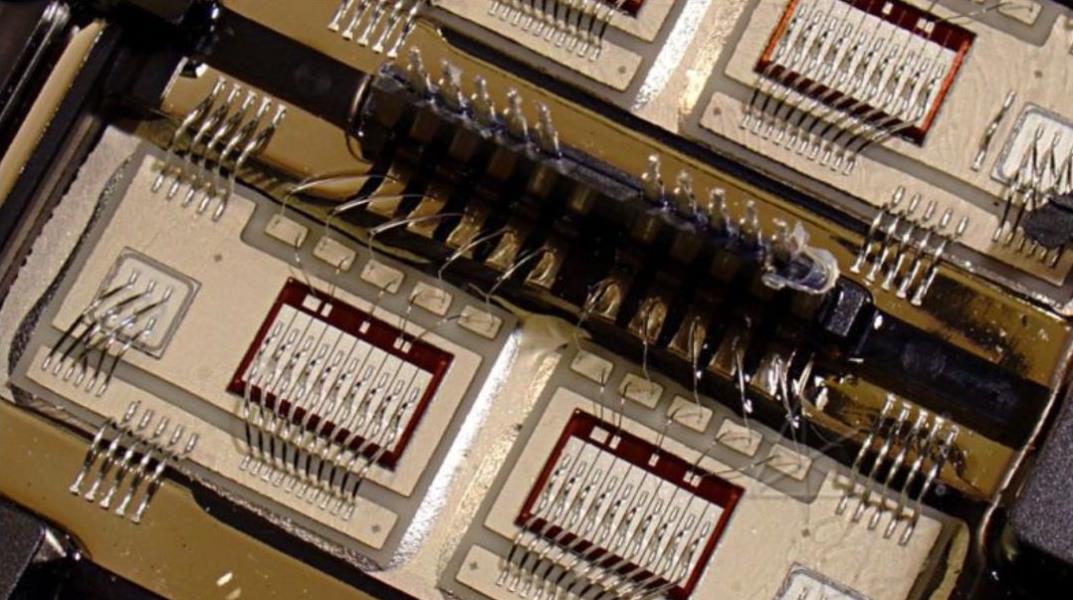

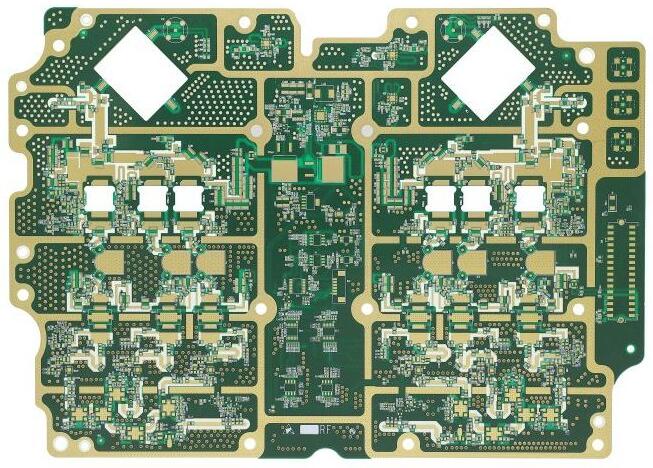

PCB board

1. The basic composition of BST

The BST circuit is constructed in accordance with the IEEE1149.1 standard, including test access channel tap and controller, instruction register IR and test data register group TDR The test access channel TAP is a 5-pin pin (1-pin is the reset terminal) connector. TAP controller is a 16 state machine, which can generate clock signals and variable control signals (ie, generate tests, transfer, capture, and update signals). This instruction or test data is transferred to the corresponding registers and controls various working states of boundary scan tests

1.1 Test the clock input terminal TCK

The TCK signal allows the boundary scan portion of the integrated circuit IC to be synchronized with the clock within the system and operate independently.

1.2 Test mode selection input TMS

The test mode selects the TMS pin as the control signal, which determines the working state of the tap controller TMS must be established before the rising edge of TCK

1.3 Test data input terminal TDI

On the rising edge of the test clock pulse TCK, the data inserted through the TDI serial array is transferred to the instruction register or the test data register, and the tap controller determines whether the shift data is instruction data or test data

1.4 Test data output terminal TDO

At the false edge of the test clock pulse TCK, data is serially output from the instruction register or test data register through TDO, and the TAP controller determines whether the serialized data is instruction or test data

2. PCB test system

2.1 Test system structure

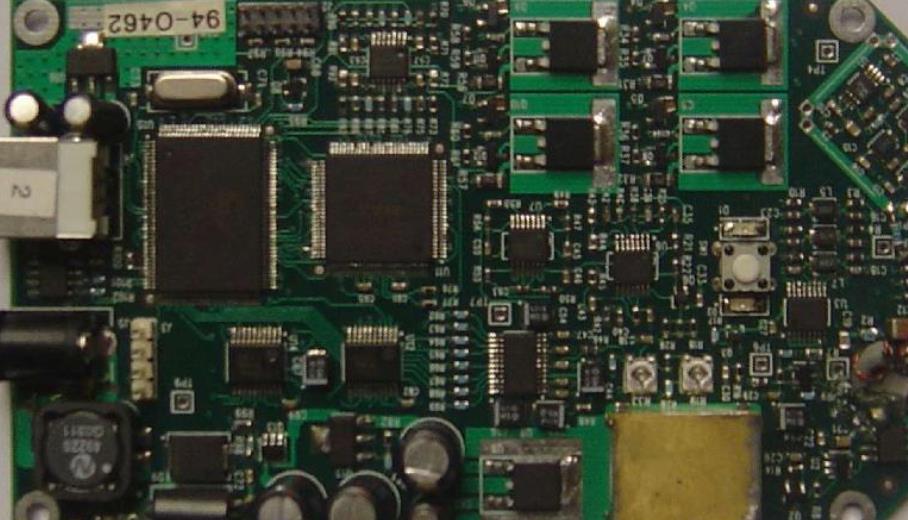

It hardware includes a general PC, a BST tester and a serial BST signal cable (a bus with 4 signals, the meaning of digital digits in the figure is as follows: 1 is TDI, 2 is TCK, 3 is TMS, and 4 is TDO) The tester is connected to the PC through the standard parallel port, and connected to the test access port tap on the PCB through the serial signal cable Suppose there are three modules A, B, and C on the printed circuit board. The module can be composed of a single chip or multiple chips They are designed according to IEEE 1149 1 Standard, that is, the BS register (the position where the dotted line passes in the module) is added to the I/chip pin, which can be used for boundary scan test If the digital system or equipment designed has multiple PCB boards, it can be connected to PCB boards through serial signal cables Users can flexibly select chips to test modules or entire PCBs through programming

2.2 Principle of test system

Testers can use PC software programming to automatically generate test patterns to detect circuit faults according to the netlist and device model of the PCB The PC shall have two boards/O pins with at least 32 bit I. In summary, 32 bit read/write pins can be formed for easy read/write operations The test software shall include preprocessor and execution unit The preprocessor reads test charts and obtains their possible relationships, resulting in a set of files, including storage and control information The execution unit loads the above file and then executes the test This process first reads the stored information, places the data on the input port, reads the data from the appropriate output port, and compares it with the expected results If a fault is found, it will generate a fault, MARK the location of the fault, and add a diagnostic program to give the specific location of the fault

2.3 Test content

1) Test the connection of the I/O pin PCB because my/O pin PCB provides access channels for the tester;

2) Test the integrity of the IC chip on the PCB The IC chip may be damaged during chip assembly The built-in self-test and internal test can be used to verify the quality of the chip;

3) Test the open circuit and short circuit faults of the IC chip connection on the PCB, which can be verified by external tests:

4) Test the integrity of the bus on the PCB, through which you can detect whether there is an open circuit fault on I/O the IC chip pin connected to the bus bar

With the continuous development of BST technology, PCB testing will gradually improve Due to the wide use of programmable integrated circuits, the flexibility and applicability of PCB board testing will be improved, and the cost of the corresponding test system will also be reduced Designers can use all programmable logic integrated Circuit PCB boards on computers. Chip logic can only be modified through software programming to produce a general-purpose printed circuit board. Therefore, PCB boards can perform different functions With this kind of pipeline, boundary scan test technology will make PCB board test more convenient and fast, and greatly reduce the test cost