表面実装アセンブリの基本構成単位であるランドは、回路基板のランド パターン、つまり特殊なコンポーネント タイプ用に設計されたさまざまなパッドの組み合わせを形成するために使用されます。 設計が不十分なパッド構造ほどイライラするものはありません。 パッド構造が正しく設計されていない場合、目的の溶接ポイントを達成することは困難であり、時には不可能ですらあります。 Pad は英語で 2 つの単語があります。Land と Pad は、しばしば交互に使用できます。 ただし、機能的には、Land は表面実装コンポーネントの 2 次元サーフェス フィーチャであり、Pad はプラグ可能コンポーネントの 3 次元フィーチャです。

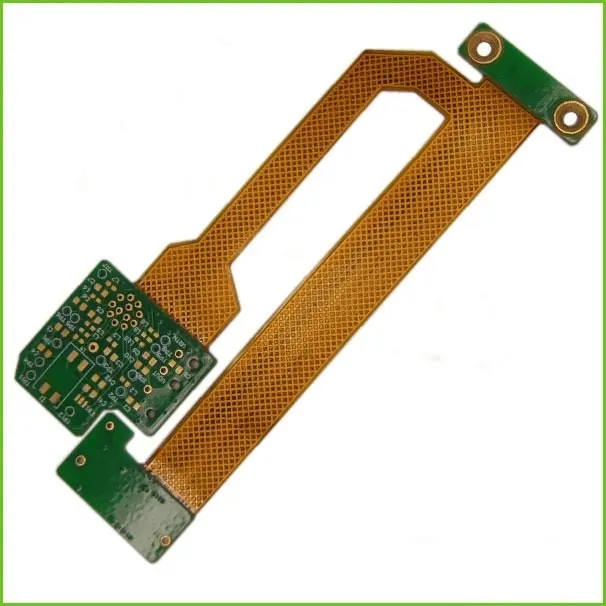

ランドには原則としてメッキスルーホール(PTH)は含まれません。 バイパス ホール (ビア) は、異なる回路層を接続するためのメッキ スルー ホール (PTH) です。 ブラインド ビアは最外層を 1 つまたは複数の内層に接続しますが、埋め込みバイパス ホールは内層のみを接続します。

前述のように、PCB 業界のパッド ランドには通常、メッキ スルー ホール (PTH) は含まれません。 パッドランド内の PTH は、溶接時にかなりの量のはんだを奪い、多くの場合、はんだ不足のはんだ接合が生成されます。 ただし、場合によっては、PCB 設計コンポーネントの配線密度がこのルールに変更せざるを得なくなります。 最も注目すべきはチップスケールパッケージ(CSP)です。 1.0mm (0.0394 ") 間隔より下では、パッドの「迷路」を介してワイヤを配線することは困難です。ブラインド バイパス ホールとマイクロ ビアがパッドに生成され、別の層への直接配線が可能になります。これらのバイパス ホールは 小さくて目立たないため、はんだを吸収しすぎないため、はんだ接合部のはんだ量にほとんどまたはまったく影響しません。

IPC (Association Connecting ElectronICs Industries)、EIA (Electronic Industry Alliance)、JEDEC (Solid State Technology Association) など、パッド構造を設計する際に使用すべき多くの業界文書があります。 主なドキュメントは IPC-SM-782 Standard for surface mount design and Pad Structure で、表面実装コンポーネントのパッド構造に関する情報を提供します。 J-STD-001 Requirements for Welding Electrical and Electronic Assemblies および IPC-A-610 Acceptability of Electronic Assemblies が溶接ポイント プロセス標準として使用される場合、パッド構造は IPC-SM-782 の意図に適合する必要があります。 パッドが IPC-SM-782 から大きくずれると、J-STD-001 および IPC-A-610 に準拠した溶接点に到達することが困難になります。

コンポーネントの知識 (つまり、コンポーネントの構造と機械的寸法) は、パッド構造設計の基本的な前提条件です。 IPC-SM-782 は、電子部品の EIA-PDP-100 登録および標準機械プロファイルと、固体および関連製品の JEDEC 95 出版登録および標準プロファイルの 2 つの構成文書を広く使用しています。 これらのドキュメントの中で最も重要なものが JEDEC 95 の出版物であることは議論の余地がありません。JEDEC 95 の出版物は最も複雑なコンポーネントを扱っているからです。 すべての登録簿の機械図面とソリッド要素の標準プロファイルを提供します。

コンポーネントの略称は、パッケージの特性、材料、端子の配置、パッケージの種類、ピンの形状、および端子の数に基づいて定義されます。 機能、材料、場所、フォーム、および数量の識別子はオプションです。

カプセル化機能: ピッチや輪郭などの機能を識別するための 1 つ以上の文字のプレフィックス。

梱包材: 本体の梱包材を識別するための 1 文字のプレフィックス。

ターミナルの場所: パッケージ アウトラインに関連するターミナルの場所を識別する 1 文字のプレフィックス。

パッケージの種類: パッケージの種類を示す 2 文字のマーク。

新しいタイプのピン: ピンの形状を確認するための 1 文字のサフィックス。

端末数: 端末数を示す 1 桁、2 桁、または 3 桁の数値サフィックス。

表面実装パッケージ機能識別子の簡単なリストには、次のものが含まれます。

E 間隔を広げます (>1.27 mm)。

F密な間隔(<0.5 mm); QFP要素に限定。

S 収縮間隔 (<0.65 mm); QFP を除くすべてのコンポーネント。

T薄型(ボディ厚1.0mm)。

PCB 表面実装用の端子位置識別子の簡単なリストには、以下が含まれます。

デュアル ピンは、正方形または長方形のパッケージの反対側にあります。

クワッド ピンは、正方形または長方形のパッケージの 4 つの側面にあります。

表面実装パッケージ タイプ識別子の簡単なリストには、次のものが含まれます。

CCチップキャリアのパッケージ構造。

FPフラットパック包装構造。

GAグリッドアレイパッケージ構造。

SOスモールアウトラインパッケージ構造。

表面実装ピンのフォーム ID の簡単なリストには、次のものが含まれます。

B ストレートハンドルまたは球状ピン構造。 これは非準拠のピン フォームです

F フラットピン構造。 これは非準拠のピン フォームです

G 翼型のピン構造。 これはコンプライアント ピン フォームです。

Jは「J」型の曲げピン構造です。 これはコンプライアント ピン フォームです。

N ピンのない構造。 これは非準拠のピン フォームです

S は「S」字型のピン構造です。 これはコンプライアント ピン フォームです。

たとえば、略語 F-PQFP-G208 は、0.5 mm (F) プラスチック (P) スクエア (Q) フラット パッケージ (FP)、ウィング ピン (G)、および端子数 208 を表します。

PCB コンポーネントと PCB 表面の特徴 (パッド構造、基準点など) の詳細な公差分析が必要です。 PCB 製造 IPC-SM-782 では、この分析の実行方法について説明しています。 多くの要素 (特に密集した要素) は、厳密なメートル単位で設計されています。 メートル系部品のインチパッド構造は設計しないでください。 蓄積された構造エラーは非互換性を引き起こし、狭い間隔のコンポーネントにはまったく使用できません。 0.65mm は 0.0256 に等しく、0.5mm は 0.0197 に等しいことを覚えておいてください。