PCBプルーフの現在の電子設計は、ほとんどが統合されたシステムレベルの設計です。 プロジェクト全体には、ハードウェア設計とソフトウェア開発の両方が含まれます。 この技術的特徴は、PCB エンジニアに新たな課題を提示します。

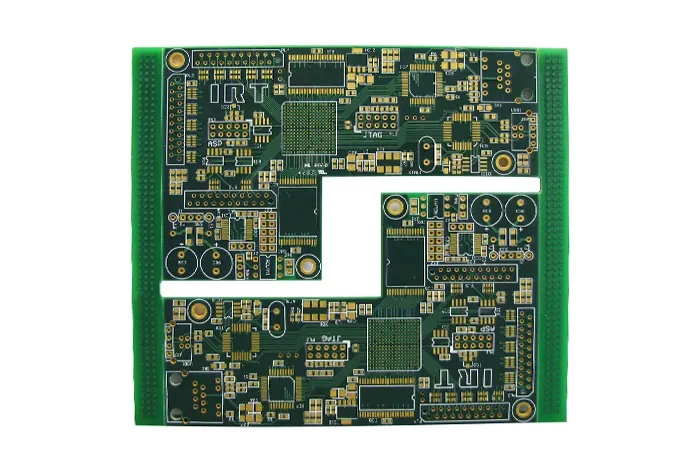

PCBプルーフ

まず、設計の初期段階でシステム ソフトウェアとハードウェアの機能を合理的に分割して、効果的な機能構造のフレームワークを形成し、冗長なサイクル プロセスを回避する方法。

次に、高性能で信頼性の高い PCB を短時間で設計する方法。 ソフトウェアの開発はハードウェアの実現に大きく依存するため、マシン全体の設計を一度パスした方が、設計サイクルをより効果的に短縮できます。 この論文では、新しい技術的背景の下でのシステム ボード レベル設計の新しい特性と戦略について説明します。

ご存知のように、電子技術の発展は日々変化しており、この変化の主な理由はチップ技術の進歩です。 半導体技術はますます物理的になり、ディープサブミクロンのレベルに達しています。 超大規模回路がチップ開発の主流となっています。 しかし、この技術と規模の変化は、電子業界全体の電子設計に多くの新しいボトルネックをもたらしました。 ボード レベルの設計にも大きな影響がありました。 最も明白な変更の 1 つは、BGA、TQFP、PLCC、およびその他のパッケージ タイプなど、多種多様なチップ パッケージです。 第二に、MCM技術の広範な適用など、製品全体の小型化を実現するための高密度ピンパッケージングと小型化パッケージングが流行しています。 さらに、チップ動作周波数の増加により、システム動作周波数の増加が可能になります。 これらの変更は、必然的にボード レベルの設計に多くの問題と課題をもたらします。 まず第一に、高密度ピンとピンサイズの物理的限界の増加により、スループットが低下します。 第 2 に、システム クロック周波数の向上によって引き起こされるタイミングとシグナル インテグリティの問題。 第 3 に、エンジニアはより優れたツールを使用して、PC プラットフォーム上で複雑で高性能な設計を完成させたいと考えています。 このことから、PCB 設計には次の 3 つの傾向があることが容易にわかります。

高速デジタル回路(高クロック周波数、高速エッジ)のPCB設計が主流となっています。

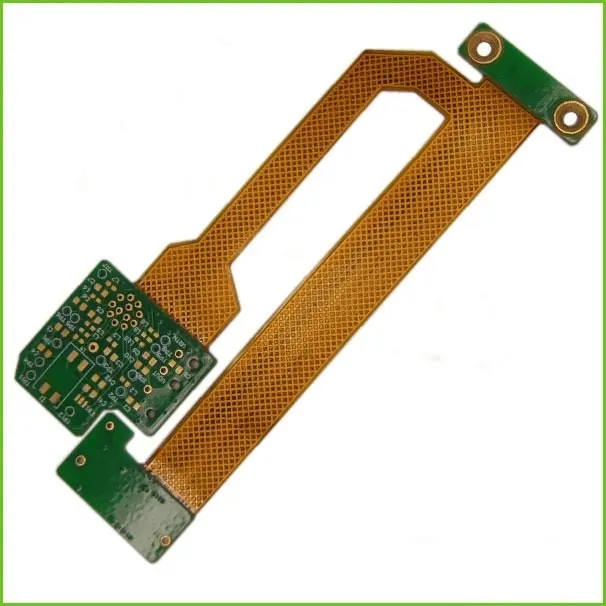

製品の小型化・高性能化には、同一基板上での混合信号設計技術(デジタル・アナログ・RF混合設計)による分配効果の問題がつきものです。

設計難易度の改善は、従来の設計プロセスと設計方法、および PC 上の CAD ツールが現在の技術的課題に対応できないことにつながります。 そのため、UNIX から NT プラットフォームへの EDA ソフトウェア ツール プラットフォームの移行は、業界で認められた傾向になっています。

基板校正用高速デジタル方式の基板ソリューション

一般に、信号相互接続遅延がエッジ信号ターンオーバーしきい値時間の 20% を超える場合、ボード上の信号ワイヤは伝送ライン効果を示します。つまり、ワイヤはもはや単純なワイヤ パフォーマンスではなく、集中した パラメータですが、分散パラメータ効果です。 この設計は高速設計です。 高速デジタル システムの設計では、設計者は寄生パラメータ (リアルタイム シーケンスとシグナル インテグリティ) によって引き起こされる誤スイッチングと信号歪みの問題を解決する必要があります。 現在、これは高速回路設計者が解決しなければならないボトルネック問題でもあります。

従来の物理ルールに基づいた PCB プルーフ

従来の高速 PCB 回路設計では、電気的ルール設定と物理的ルール設定が分離されていることがわかります。 これにより、次の不具合が発生します。

PCB 設計の初期段階では、エンジニアは詳細なフロントエンドとバックエンド (つまり、論理構成の物理的な実装) の分析に多くのエネルギーを費やさなければならず、電気的要件を満たす物理配線戦略を計画する必要がありました。

高速化は複雑な課題であり、配線や平行線の長さを制御するだけでは実現できません。

設計者は、虚偽の要素を含む物理的なルールが実際の配線に適用されず、ルールを実用化するために何度も修正しなければならないというジレンマに直面することは避けられません。

配線が完了したら、ポスト検証ツールを分析に使用できます。 ただし、問題が見つかった場合は、設計に戻って構造やルールを調整する必要があります。 これは循環冗長プロセスです。 それは必然的に市場投入までの時間に影響を与えます。

設計に含まれる重要なネットワークが数個または数十個しかない場合は、物理的なルール ドリブンで設計タスクを十分に完了できます。 しかし、設計に数百または数千ものワイヤ ネットワークが存在する場合、物理的なルールに基づく方法は、設計作業にはまったく適していません。 電子技術の発展には、設計が直面するボトルネックの問題を解決するための新しい方法とツールが必要です。 物理法則主導の高速設計の欠点を解決するために、高速デジタル回路設計 EDA ツールの研究開発に携わる業界の知識豊富な人々は、リアルタイムの電気法則主導の物理レイアウトとルーティング 3 のアイデアを提唱しました。 数年前、高速デジタルの設計思想を一新。

PCB設計

新しい電気的ルール主導の PCB プルーフ: 相互接続合成

相互接続合成は、リアルタイムの電気的規則駆動方式の典型的な用語です。つまり、物理的なレイアウトとルーティングのプロセスで、相互接続シンセサイザーが電気的規則の制約に従ってリアルタイムで分析し、要件を満たすルーティング戦略を抽出します。 設計を一挙に成功させます。 この方法は、相互接続合成を通じて電気的要件と物理的実現を正確に統合し、物理的ルール駆動方法の欠点を根本的に排除します。

PCB プルーフ相互接続の統合プロセスは次のとおりです。

ツールにノイズ制約と時間順序制約ルールを入力します。

タイミング制約を満たすためのタイミング制御レイアウト。

最適化前にシグナル インテグリティを実行します。

ボード レベルの統合により、キー ライン ネットワークが電気的要件を満たしていることを確認します。

通常のワイヤー ネットワークの配線を完了します。

ケーブル配線の包括的な最適化。

電気的ルール駆動法は、レイアウトとルーティングを設計する前に品質を効果的に評価し、信号の歪みを検出し、整合ネットワーク トポロジと適切な端子整合構造と抵抗値を決定できます。 レイアウトと配線が完了したら、事後検証を行い、ソフトウェアオシロスコープで波形を直感的に検出できます。 このとき見つかったタイミングや歪みの問題は、配線総合最適化機能で解決できます。

PCBプルーフゴールドツールの組み合わせと設計プロセス

現在、多くの EDA メーカーが高速システム PCB 設計用の EDA ツールを提供しており、ユーザーがこの分野で設計品質を効果的に向上させ、設計サイクルを短縮するのに役立ちます。 電気的ルール駆動方式を適用したEDAシステムボードレベルツールの中で最も代表的なのがMentorGraphICs ICXソフトウェアパッケージです。 相互接続統合の概念を提唱した最初の製品であり、業界で最も成熟したツールの組み合わせでもあります。 このソフトウェア パッケージは、現在業界で普及しているプラグ アンド プレイの特性を備えています。 多くのメーカーの PCB の従来の EDA 設計プロセスに統合できます。

PCB プルーフ用の混合信号設計ソリューション

デザインの小型化が流行する中、消費者は高性能で低価格な商品を求めています。 市場競争に適応するために、製造業者は研究開発担当者が市場を占有するために可能な限り短い時間でさまざまなタイプと機能構成の高性能で低コストの製品を開発することを必要としています。 これは、設計者に多くの新しい設計課題をもたらします。 例えば、デジタル・アナログ混合技術、さらにはRF技術を同一基板上で使用することで、設計の小型化や製品機能の向上という目的を達成します。 世界中で普及している携帯電話がその典型です。 業界には対応するソリューションもあります。設計チーム、並行設計、派生、および設計の再利用が最も典型的な戦略です。

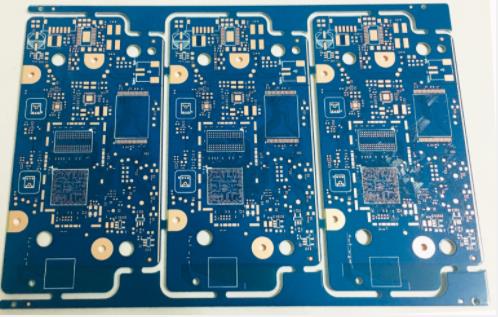

PCB プルーフの従来のシリアル設計

つまり、PCB エンジニアがすべてのフロントエンド回路設計を完了した後、彼はそれを物理ボード レベルの設計者に転送して、バックエンドの実装を完了します。 設計サイクルは、回路設計とボード レベルの設計時間の合計です。 小型化が主流の設計思想になり、ハイブリッド技術が広く採用された後、シリアル設計方法は遅れをとっています。 タイムリーなリストの要件を満たすために、設計方法を革新し、強力な EDA ツールを使用して設計者を支援する必要があります。 誰もが知っているように、私たち一人一人がすべての分野の専門家になることは不可能であり、短時間ですべての作業を最善かつ最速で完了することは不可能です。 設計チームの概念は、この文脈で提唱され、広く適用されてきました。 現在、多くの企業がデザインチーム方式で製品開発に協力しています。 つまり、設計の複雑さとさまざまな機能モジュールに応じて、設計全体がさまざまな機能ブロックブロックに分割され、さまざまな設計者と開発者が論理回路とPCBボードを並行して設計します。 次に、デザインの最上位レベルで、各ブロック ブロックの最終的なデザイン結果が「デバイス」として呼び出され、ボード デザイン全体が形成されます。 この方法は、PCB 設計の再利用と呼ばれます。 この方法により、設計サイクルを大幅に短縮できることがわかります。 設計時間は、最も時間がかかる BLOCK ブロックの設計時間と、バックエンド インターフェイス接続処理の時間の合計のみです。

PCB校正ツールの標準化とサードパーティ製ツールの統合

現在、主要な EDA ツール サプライヤとして、Cadence、Synopsis、MentorGraphics など、多くのメーカーが PCB 設計自動化 (EDA) ツールの開発に取り組んでいます。 また、他にも多くの EDA メーカーがあります。 EDAは、ネットワーク、通信、コンピュータ、航空宇宙など幅広い分野をカバーしています。製品には、システムボード設計、システムデジタル/IFアナログ/デジタルアナログハイブリッド/RFシミュレーション設計、システムIC/ASIC/FPGA設計/シミュレーション/ 検証、ソフトウェアとハードウェアの共同設計など。どの EDA サプライヤも、さまざまなユーザーのさまざまな設計ニーズを満たす最強の設計プロセスを提供することは困難です。 市場シェアの観点から、Cadence の強力な製品は IC ボードの設計とサービス、Synopsis の強力な製品は論理合成、MentorGraphics の強力な製品は PCB 設計とディープ サブミクロン IC 設計の検証とテストです。 現代の電子設計がますます EDA ツールと技術に依存していることは間違いありません。 EDA メーカーは、ユーザーのニーズを満たすために製品標準化の方法を採用しています。 多くのデザイナーは、複数の企業の強力な製品を自社のデザイン プロセスに採用して、最適なデザイン プロセスを形成しています。 EDA メーカーは、自社の強力な製品の互換性と、サードパーティ製品を統合してユーザーの潜在的なニーズを満たす能力を向上させてきました。

PCBプルーフの導出技術

民生用製品に焦点を当てている PCB メーカーは、さまざまなレベルのユーザーのニーズを満たすために、市場を占有するためにさまざまな機能とグレードの製品を開発する必要があることがよくあります。 これまでは、機能の異なる製品を開発するために設計プロセスを変える、つまり、機能の異なる基板を異なる設計データで作り、製品を実現することが多かった。 不利な点は、コストが増加し、設計サイクルが長くなり、製品の人為的な信頼できない要因が増加することです。 現在、多くのメーカーが派生技術を使用して上記の問題を解決しています。つまり、同じ設計プロセス データから異なる機能シリーズの製品を派生させて、コストを削減し、品質を向上させています。 ユーザーのニーズを満たすために、多くの EDA メーカーは、MentorGraphics の boardstation や Zuken Redac などの自社製品に Derived Rule Check (DRC) 機能を追加しています。 フロントエンドの回路設計における派生機能モジュールのバックエンドでの物理的なレイアウト ルール チェックへの割り当て、さまざまな派生製品のコンポーネント リスト テーブルの生成、生産および加工データ、写真図面データおよび加工組立図など、したがって、 この種の PCB 設計パズルを完全に終わらせます。